SimPPC jest symulatorem mikroprocesora PowerPC 601, pierwszego przedstawiciela rodziny PowerPC. Opracowany w formie aplikacji działającej pod Windows XP symulator przybliża budowę PowerPC 601, a także demonstruje działanie rozkazów tego mikroprocesora.

Aplikacja SimPPC została zrealizowana w środowisku Borland C++ Builder Personal 6.0 w 2005 r. Po ośmiu latach została ona poddana znaczącej modyfikacji. Zmiany objęły sposób działania symulowanego mikroprocesora, a także wygląd interfejsu użytkownika (GUI). Zwiększona została również stabilność działania aplikacji oraz ilość wykonywanych przez nią operacji. W porównaniu do pierwowzoru uproszczona została składnia rozkazów symulowanego mikroprocesora i jest ona zasadniczo zgodna ze standardem IBM. Udoskonalona w ten sposób aplikacja SimPPC w wersji 1.1 została udostępniona dla szerokiego kręgu odbiorców wraz ze źródłami w formie wolnego i otwartego oprogramowania.

Budowa mikroprocesora PowerPC 601

Mikroprocesor PowerPC 601, którego działanie symuluje aplikacja SimPPC, jest 32-bitową implementacją architektury PowerPC. Jest on superskalarnym mikroprocesorem RISC, a w jego budowie wyróżnić można następujące elementy.

- Jednostka rozkazowa (Instruction Unit) – jest odpowiedzialna za pobieranie rozkazów z pamięci notatnikowej i rozdzielanie ich między poszczególnymi jednostkami wykonawczymi. Jednostka rozkazowa składa się z kolejki rozkazów (Instruction Queue), układu rozdzielania rozkazów (Issue Logic) i jednostki skokowej BPU.

- Jednostka skokowa BPU (Branch Processing Unit) – wykonuje rozkazy skoków, w taki sposób, aby uniknąć opóźnień (tzw. zero cycle branch). W przypadku rozkazów skoku warunkowego wykonywana jest predykcja skuteczności wykonania skoku, zgodnie z którą pobierane są kolejne rozkazy. W wykonywaniu rozkazów skoku bierze udział rejestr warunków CR (Condition Register), a także rejestr adresu śladowego LR (Link Register) i licznik CTR (Count Register). Wchodzące w skład BPU rejestry CR, LR i CTR są rejestrami 32-bitowymi.

- Jednostka całkowitoliczbowa IU (Integer Unit) – wykonuje rozkazy arytmetyczne i logiczne na liczbach całkowitych, rozkazy komunikacji z pamięcią (Load, Store), a także rozkazy ładowania i zapamiętywania danych zmiennopozycyjnych. Jednostka całkowitoliczbowa składa się z jednostki arytmetyczno-logicznej (ALU), układu mnożenia i dzielenia całkowitego, a także bloku 32 rejestrów ogólnego przeznaczenia GPR (General Purpose Registers) oraz rejestru wyjątków XER (Integer Exception Register). Wszystkie wymienione rejestry są 32-bitowe.

- Jednostka zmiennopozycyjna FPU (Floating Point Unit) – odpowiedzialna za wykonywanie rozkazów zmiennopozycyjnych na danych zgodnych ze standardem IEEE 754. Jednostka zmiennopozycyjna składa się z bloku 32 rejestrów zmiennopozycyjnych FPR (Floating Point Registers), które są rejestrami 64-bitowymi. Dzięki wyposażeniu FPU w odpowiednie układy kombinacyjne, operacje dodawania, mnożenia i dzielenia wykonywane są sprzętowo. Jednostka ta ma też wbudowany 32-bitowy rejestr stanu i sterowania FPSCR (Floating Point Status and Control Register).

Mikroprocesor PowerPC 601 może pracować w dwóch trybach, a mianowicie w trybie uprzywilejowanym (Supervisor Level) lub w trybie nieuprzywilejowanym (User Level), zwanym też trybem użytkownika. Tryb pracy określa zakres możliwych do wykonania rozkazów oraz dostępnych rejestrów.

- Rejestry trybu nieuprzywilejowanego – używane w obu trybach pracy mikroprocesora. Zalicza się do nich rejestry GPR, FPR, CR, FPSCR oraz rejestry specjalne trybu użytkowego – CTR, XER, LR, a także rejestr zegara czasu rzeczywistego RTC (Real-Time Clock, złożony z dwóch 32–bitowych części, tj. górnej RTCU i dolnej RTCL) oraz rejestr MQ. Ten ostatni jest 32–bitowym rejestrem stosowanym w operacjach mnożenia, dzielenia oraz przesunięć długich. Rejestr MQ jest dla PowerPC 601 i nie występuje w innych modelach, gdyż nie jest zdefiniowany w architekturze PowerPC.

- Rejestry trybu uprzywilejowanego – dostępne tylko w trybie uprzywilejowanym. Zalicza się do nich rejestr stanu procesora MSR (Machine State Register), rejestry segmentowe SR (Segment Registers) i rejestry specjalne trybu uprzywilejowania SPR (Supervisor-Level Special Purpose Registers).

Ponadto PowerPC 601 posiada wewnętrzną pamięć notatnikową (cache) o rozmiarze 32KB, która jest zarówno pamięcią rozkazów, jak i danych, oraz jednostkę zarządzania pamięcią MMU (Memory Management Unit), która pozwala na segmentowo-stronicową organizację pamięci wirtualnej.

Mikroprocesor PowerPC 601 został wprowadzony na rynek jesienią 1993 r. Egzemplarze produkowane przez firmę Motorola nosiły oznaczenie MPC601, podczas gdy jednostki IBM określone były jako PPC601 (fot. http://www.thocp.net).

Mikroprocesor PowerPC 601 ma dwie zewnętrzne magistrale, a mianowicie 64-bitową magistralę danych i 32-bitową magistralę adresową. Napięcie zasilania wynosi 3,6V, a moc rozpraszana 6,5W w przypadku częstotliwości 50MHz i 8,5W dla taktowania 66MHz. PowerPC 601 przeznaczony był do stosowania w stacjach roboczych, jak i w symetrycznych systemach wieloprocesorowych. W wersji 66MHz jego wydajność w SPECfp wynosiła 80.

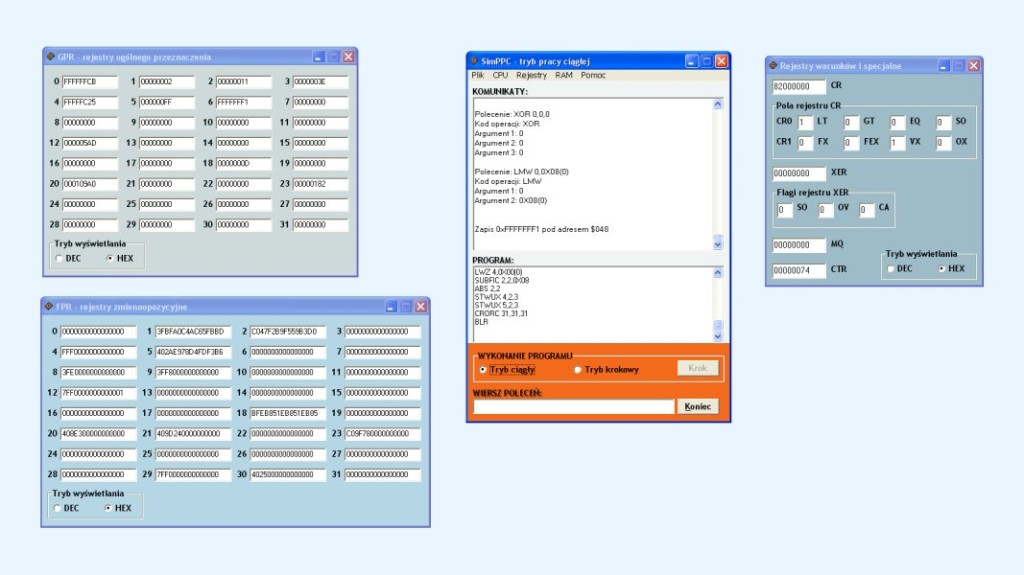

Zasoby PowerPC odwzorowane w SimPPC

SimPPC jest programowym symulatorem mikroprocesora PowerPC 601. Symulator ten został wykonany w postaci aplikacji dla systemu operacyjnego Windows XP. W SimPPC zostały odwzorowane

- rejestry GPR (GPR0 – GPR31),

- rejestry FPR (FPR0 – FPR31),

- rejestr warunków CR, rejestr wyjątków XER oraz rejestr MQ i licznik CTR,

- rejestr FPSCR.

Do dyspozycji użytkownika jest również pamięć RAM o rozmiarze 4KB, która pełni rolę pamięci danych. Stan wymienionych wyżej rejestrów oraz pamięci RAM zaprezentowany jest na odpowiednich formularzach. Oprócz śledzenia aktualizowanego na bieżąco stanu symulowanych zasobów, użytkownik ma też możliwość wprowadzania wartości do rejestrów oraz pamięci RAM. Służą do tego pola edycji oraz przyciski dostępne na poszczególnych formularzach.

Rozkazy i mnemoniki

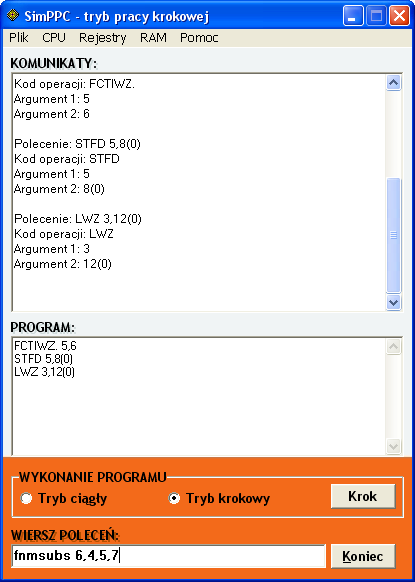

Aplikacja SimPPC umożliwia wykonanie podzbioru rozkazów mikroprocesora PowerPC 601. Wersja 1.1 opisywanej aplikacji symuluje działanie łącznie 315 rozkazów, wliczając w to warianty podstawowych operacji (np. ADDE, ADDE., ADDEO, ADDEO.). Wśród realizowanych przez SimPPC instrukcji znajdują się rozkazy wykonywane przez każdą z trzech jednostek wykonawczych (tj. BPU, IU, FPU), a w szczególności operacje:

- arytmetyczno-logiczne wykonywane na liczbach całkowitych,

- arytmetyki zmiennopozycyjnej,

- ładowania i zapamiętywania danych w pamięci RAM,

- skoków warunkowych oraz bezwarunkowych.

Aplikacja daje także możliwość wykonania ekstrakodu – dodatkowych operacji, które nie są rozkazami PowerPC 601. Wśród nich są niektóre mnemoniki wchodzące w skład asemblera opracowanego przez IBM dla mikroprocesorów PowerPC oraz operacje charakterystyczne dla SimPPC. Ekstrakod umożliwia szybkie i bezpośrednie wprowadzenie danych do poszczególnych rejestrów oraz pamięci RAM.

Jedną z najważniejszych funkcji SimPPC jest możliwość wczytanie programów zapisanych w plikach tekstowych i wykonania ich w sposób ciągły lub krokowy. Programy te muszą być napisane w quasi-asemblerze SimPPC, który jest oparty na wspomnianym już asemblerze IBM dla PowerPC.

Główny formularz aplikacji SimPPC w wersji 1.1.

W trakcie wykonywania rozkazów lub mnemoników użytkownik ma możliwość obserwacji zmian wartości w rejestrach lub pamięci RAM. Zmiany te są sygnalizowane chwilową zmianą koloru elementów poszczególnych formularzy, które przedstawiają stan symulowanego mikroprocesora oraz pamięci RAM.

Dystrybucja

Aplikację SimPPC można pobrać z niniejszej witryny wraz z podręcznikiem użytkownika oraz plikami źródłowymi udostępnionymi na licencji GPLv2. Projekt ten może być pomocny w zapoznaniu się z architekturą PowerPC lub też stać się źródłem inspiracji dla opracowania kolejnych aplikacji przybliżających zagadnienia z dziedziny techniki mikroprocesorowej oraz programowania niskopoziomowego.

Do pobrania

SimPPC, symulator mikroprocesora PowerPC 601

SimPPC – aplikacja w wersji 1.1 wraz z bibliotekami BPL potrzebnymi do jej uruchomienia

Podręcznik użytkownika – instrukcja obsługi SimPPC w wersji 1.1

Pliki źródłowe – archiwum zawierające projekt SimPPC w wersji 1.1 dla BC++ 6.0

Dokumentacja mikroprocesora PowerPC 601

AIX 5L for POWER-based Systems. Assembler Language Reference, Second Edition (April 2001), IBM Corp.

PowerPC™ 601 RISC Microprocessor User’s Manual, MPC601UM/AD, Motorola Inc. 1995

PowerPC® Microprocessor Family: The Programming Environments Manual for 64-bit Microprocessors, Version 3.0, July 15, 2005, IBM Systems and Technology Group